# WD5125C

# 2.5A Buck-Boost Converters with I<sup>2</sup>C Interface

# **Descriptions**

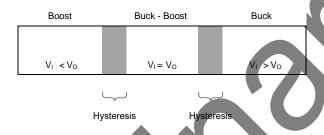

The WD5125C is a high efficiency, high output current buckboost converter fully programmable through I<sup>2</sup>C. Depending on the input voltage, it can automatically operate in boost, buck or in a novel 4-cycle buck-boost mode when the input voltage is approximately equal to the output voltage. The transitions between modes happen at defined thresholds and avoid unwanted toggling within the modes to reduce output voltage ripple. Two registers, accessible through I<sup>2</sup>C, set the output voltage, and a VSEL pin selects which output voltage register is active. Thus the devices can support dynamic voltage scaling. If the output voltage register is changed during operation or the VSEL pin is toggled, the device transits in a defined, programmable ramp-rate.

The WD5125C is available in a 2.2mm×1.3mm CSP-15L package. Standard products is Pb-Free and Halogen-Free.

#### **Features**

- Input Voltage Range: 2.2V to 5.5V

- Output voltage range: 1.8 V to 5.2 V

- ♦ I<sup>2</sup>C-configurable during operation and shutdown

- ♦ VSEL pin to toggle between two output voltage presets

- Current mode buck-boost architecture

- Defined transitions between buck, buck-boost and boost operation

- ◆ Forward and reverse current operation

- Start-up into pre-biased outputs

- Safety and robust operation features

- Integrated soft start

- ◆ Overtemperature and VINOV protection

- ◆ True load disconnect during shutdown

- Forward and backward current limit

- Pre-programmed output voltages (3.3 V, 3.45 V)

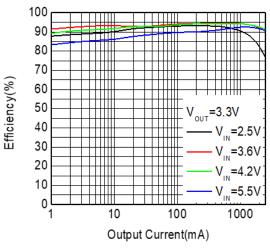

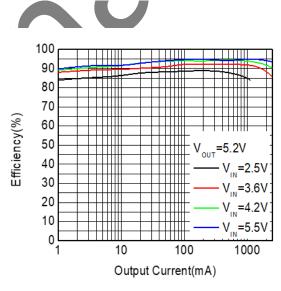

- High efficiency over entire load range

- ♦ Low 13 μA operating quiescent current

- Automatic power save mode and forced PWM mode (I<sup>2</sup>C-configurable)

#### http://www.ovt.com/

#### CSP-15L

Pin configuration (Top view)

= Device code

= Special code

= Year code

V = Week code

Marking

#### **Applications**

- System pre-regulator

- Point-of-load regulation

- Thermoelectric device supply

- Broadband network radio or SoC supply

### **Order information**

| Device         | Package | Shipping       |

|----------------|---------|----------------|

| WD5125C -15/TR | CSP-15L | 3000/Reel&Tape |

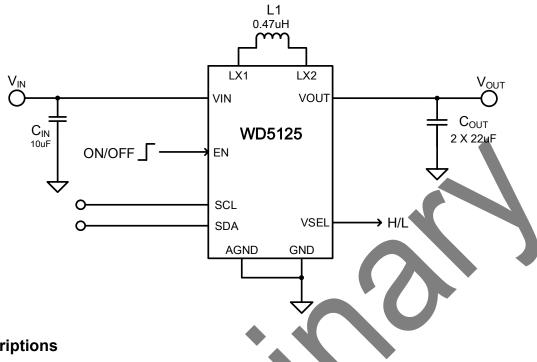

# **Typical Applications**

# **Pin Descriptions**

| Pin NO.    | Symbol | I/O | Descriptions                                                                    |

|------------|--------|-----|---------------------------------------------------------------------------------|

| A 4        | -N     |     | Device enable. A high logic level on this pin enables the device; a low logic   |

| A1         | EN     | I   | level on this pin disables the device.                                          |

| A2         | VIN    | _   | Supply voltage for power stage                                                  |

| A3         | VIN    | _   | Supply voltage for power stage                                                  |

|            |        |     | This pin selects which VOUT register is active. When a low logic level is       |

| B1         | VSEL   | I   | applied to this pin, the VOUT1 register sets the output voltage. When a high    |

|            |        |     | logic level is applied to this pin, the VOUT2 register sets the output voltage. |

| B2         | LX1    | 14  | Inductor connection                                                             |

| В3         | LX1    | _   | Inductor connection                                                             |

| C1         | AGND   | -   | Analog ground                                                                   |

| C2         | GND    | 7   | Power ground                                                                    |

| C3         | GND    |     | Power ground                                                                    |

| D1         | SCL    | I/O | I2C serial interface clock. Pull this pin up to the I2C bus voltage with a      |

| וט         | SCL    | 1/0 | resistor or a current source.                                                   |

| D2         | LX2    |     | Inductor connection                                                             |

| D3         | LX2    | _   | Inductor connection                                                             |

| E1         | SDA    | I/O | I2C serial interface data. Pull this pin up to the I2C bus voltage with a       |

| <b>□</b> I | SDA    | 1/0 | resistor or a current source.                                                   |

| E2         | VOUT   | _   | Converter output                                                                |

| E3         | VOUT   |     | Converter output                                                                |

**OMNIVISION**

Mar. 2021 - Rev. 0.7

Tel: + 1 408 567 3000 Fax: + 1 408 567 3001

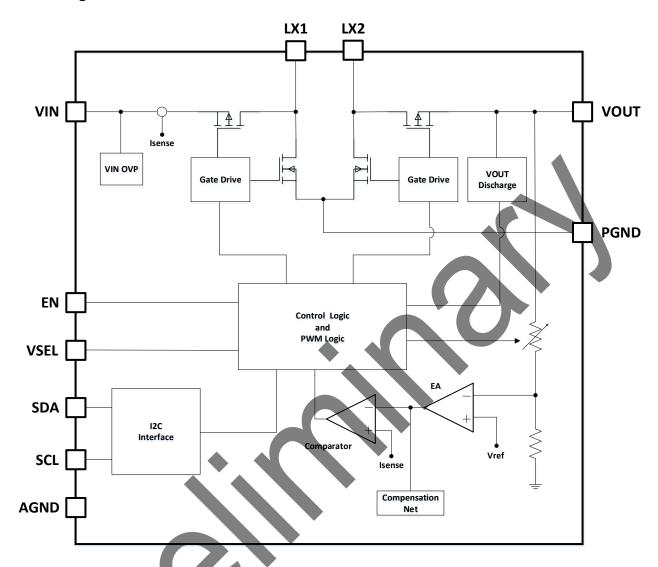

# **Block Diagram**

# **Absolute Maximum Ratings**

| Parameter                         | Symbol                                  | Value           | Unit  |

|-----------------------------------|-----------------------------------------|-----------------|-------|

| Farameter                         | Symbol                                  | value           | Offic |

| Input voltage                     | VIN, LX1, LX2, VOUT, SCL, SDA, EN, VSEL | <b>-</b> 0.3∼+6 | V     |

| Input voltage for less than 10 ns | LX1, LX2                                | -3∼9            | V     |

| Thermal Characteristics (1)       | ReJA                                    | 80.5            | °C/W  |

| Thermal Characteristics (1)       | Rejc                                    | 0.6             | °C/W  |

| Maximum Junction Temperature      | TJ                                      | 150             | °C    |

| Operating Ambient Temperature     | Topr                                    | -40 ~ 85        | °C    |

| Storage Temperature               | Tstg                                    | -65 ~ 150       | °C    |

| CCD Classification                | НВМ                                     | ±2000           | V     |

| ESD Classification                | CDM                                     | ±500            | V     |

Tel: + 1 408 567 3000 Fax: + 1 408 567 3001

# Recommended Operation Conditions (2)

| Symbol          | Characteris                       | Min.                                         | Тур.  | Max. | Unit  |    |

|-----------------|-----------------------------------|----------------------------------------------|-------|------|-------|----|

| V <sub>IN</sub> | Supply Voltage                    |                                              | 2.2   |      | 5.5   | V  |

| Vout            | Output Voltage                    | Low range                                    | 1.8   |      | 4.975 | V  |

| <b>V</b> 001    | Output Voltage                    | High range                                   | 2.025 |      | 5.2   | V  |

| V <sub>IH</sub> | High-level input voltage          | SCL, SDA, VSEL                               | 1.3   |      | Vin   | V  |

| VIL             | Low-level input voltage           | SCL, SDA, VSEL                               | 0     |      | 0.3   | V  |

| VEN             | Input voltage                     | 0                                            |       | Vin  | V     |    |

|                 |                                   | $V_0 = 3.3 \text{ V}, V_1 \ge 2.5 \text{ V}$ |       |      | 2.3   |    |

| lo              | Output current                    | $V_0 = 3.5 \text{ V}, V_1 \ge 2.5 \text{ V}$ |       | 1    | 2     | Α  |

| 10              |                                   | $V_0 = 3.5 \text{ V}, V_1 \ge 2.8 \text{ V}$ |       |      | 2.5   | A  |

|                 |                                   | $V_0 = 3.3 \text{ V}, V_1 \ge 3 \text{ V}$   |       |      | 3     |    |

| Cin             | Input capacitance, effective valu | е                                            | 5     |      |       | μF |

| Co              | Output capacitance, effective va  | lue                                          | 13    | 16   |       | μF |

| L               | Inductance, effective value       | 0.39                                         | 0.47  | 0.56 | μH    |    |

| T <sub>A</sub>  | Operating free-air temperature    | -40                                          | -     | 85   | ℃     |    |

| TJ              | Operating junction temperature    |                                              | -40   |      | 125   | °C |

These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

Note 1: Surface mounted on FR-4 Board using 1 square inch pad size, dual side, 1oz copper.

Note 2: The device is not guaranteed to function outside of its operating conditions.

Tel: + 1 408 567 3000

Fax: + 1 408 567 3001 www.ovt.com

# **Electronics Characteristics**

$V_{IN}$  = 3.6 V,  $V_{OUT}$  = 3.3 V, Typical values are at  $T_J$  = 25°C, unless otherwise noted.

| PARAMETER              |                                             |                  | TEST CONDITIONS                                                                           | MIN   | TYP   | MAX   | UNIT |

|------------------------|---------------------------------------------|------------------|-------------------------------------------------------------------------------------------|-------|-------|-------|------|

| SUPPLY A               | AND THERMAL PROTECT                         | ION              |                                                                                           |       |       |       |      |

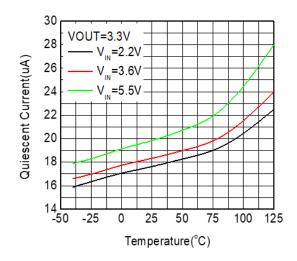

|                        |                                             |                  | $V_{I}$ = 3.6 V, $V_{O}$ = 3.3 V, $V_{(EN)}$ = 3.6 V, not switching                       |       | 18    |       | μA   |

| $I_{Q-VIN}$            | Supply current into VIN                     |                  | V <sub>I</sub> = 3.6 V, V <sub>O</sub> = 0 V, V <sub>(EN)</sub> = 3.6 V, Output           |       | 40    |       |      |

|                        |                                             |                  | disabled with ENABLE bit in Control Register                                              |       | 13    |       | μA   |

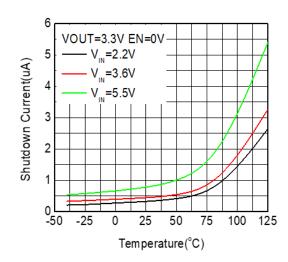

| I <sub>SD</sub>        | Shutdown current into VIN                   | I                | V <sub>I</sub> = 3.6 V, V <sub>O</sub> = 0 V, V <sub>(EN)</sub> = 0 V                     |       | 0.8   |       | μΑ   |

| $V_{\text{IT+}}$       | Under-voltage lockout three                 | eshold           | V <sub>UVLO</sub> rising                                                                  | 2     | 2.1   | 2.2   | V    |

| V <sub>IT-HYS</sub>    | UVLO threshold voltage h                    | ysteresis        | V <sub>UVLO-HYS</sub>                                                                     |       | 150   |       | mV   |

| T <sub>OTP</sub>       | Thermal shutdown temper                     | rature           | Junction temperature rising                                                               |       | 155   |       | °C   |

| T <sub>OTP-HYS</sub>   | Thermal shutdown hystere                    | esis             |                                                                                           |       | 20    |       | °C   |

| I/O SIGNA              | ALS                                         |                  |                                                                                           |       |       |       | ı    |

|                        | Positive-going input                        | SCL, SDA, VSEL   |                                                                                           |       |       | 1.17  |      |

| V <sub>IT+</sub>       | threshold voltage                           | EN               |                                                                                           | 1.07  | 1.1   | 1.13  | V    |

|                        | Negative-going input                        | SCL, SDA, VSEL   |                                                                                           | 0.42  |       |       | _    |

| $V_{\text{IT-}}$       | threshold voltage                           | EN               |                                                                                           | 0.97  | 1     | 1.03  | V    |

| V <sub>HYS</sub>       | Hysteresis voltage                          | EN               | * . * . * . * . * . * . * . * . * . * .                                                   | 40    |       |       | mV   |

| I <sub>IH</sub>        | High-level input current                    | SCL, SDA, VSEL   | V <sub>(SCL)</sub> = V <sub>(SDA)</sub> = V <sub>(VSEL)</sub> = 1.8 V, no pullup resistor |       | ±0.01 | ±0.1  | _    |

| I <sub>IL</sub>        | Low-level input current                     | SCL, SDA, VSEL   | $V_{(SCL)} = V_{(SDA)} = V_{(VSEL)} = 0 \text{ V, no pullup resistor}$                    |       | ±0.01 | ±0.1  | μA   |

| loL                    | Low-level output current                    | SCL, SDA         | V <sub>OL</sub> = 0.4 V                                                                   | 8     |       |       | mA   |

| I <sub>IB</sub>        | Input bias current                          | EN               | V <sub>(EN)</sub> = 0 V to 5.5 V                                                          |       | ±0.01 | ±0.1  | μΑ   |

| POWER S                | STAGE                                       |                  |                                                                                           |       |       |       | I    |

|                        |                                             |                  | Low range                                                                                 | 1.8   |       | 4.975 |      |

|                        | Output voltage range                        |                  | High range                                                                                | 2.025 |       | 5.2   | V    |

| .,                     | 0 1 1 1                                     |                  | PWM operation                                                                             | -1.5  |       | 1.5   | 0/   |

| Vo                     | Output voltage accuracy                     |                  | PSM operation                                                                             | -1.5  |       | 3.5   | %    |

|                        |                                             | 105 0)           | VSEL = low                                                                                |       | 3.3   |       | .,   |

|                        | Default output voltage (RA                  | ANGE = 0)        | VSEL = high                                                                               |       | 3.45  |       | V    |

|                        |                                             |                  | V <sub>I</sub> = 2.9 V, V <sub>O</sub> = 3.6 V,                                           | F 0   |       | 0.5   |      |

|                        |                                             |                  | boost operation, output sourcing current                                                  | 5.2   |       | 6.5   |      |

|                        |                                             |                  | V <sub>I</sub> = 4.1 V, V <sub>O</sub> = 3.3 V,                                           | 0.0   | 4.0   | 5.0   | 1    |

| I <sub>LIMIT</sub>     | Switch current limit                        |                  | buck operation, output sourcing current                                                   | 3.8   | 4.3   | 5.2   | Α    |

|                        |                                             |                  | V <sub>I</sub> = 5 V, V <sub>O</sub> = 3.3 V,                                             | 4.0   |       | 0.25  |      |

|                        |                                             |                  | reverse-boost operation, output sinking current                                           | -1.3  |       | -0.35 |      |

| I <sub>T-(PSM)</sub>   | PSM entry threshold (peal                   | k) current       | V <sub>I</sub> = 4.2 V; V <sub>O</sub> = 3.3 V                                            |       | 0.85  |       | Α    |

| IDISCHARGE             | Output discharge current                    |                  | $V_1 = 3.6 \text{ V}, V_0 \ge 0.8 \text{ V}$                                              | 50    |       |       | mA   |

| VT+(PG)                | Positive-going power-good threshold voltage |                  |                                                                                           |       | 95    |       | %    |

| VT-(PG)                | Negative-going power-good threshold voltage |                  |                                                                                           |       | 90    |       | 70   |

| $V_{INOV}$             | Positive-going input over                   | oltage threshold |                                                                                           |       | 5.7   |       | V    |

| I <sup>2</sup> C INTER | RFACE                                       |                  |                                                                                           |       |       |       |      |

|                        |                                             |                  |                                                                                           |       |       |       |      |

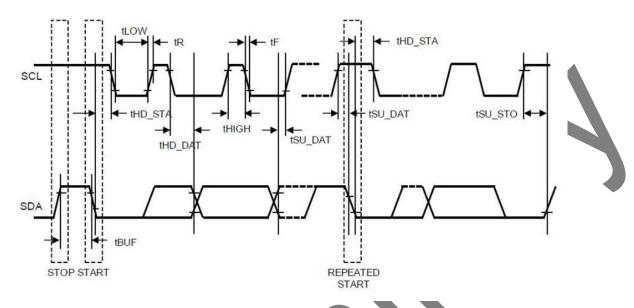

# **Timing Requirements**

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted)

|                       | PARAMETER                             | TEST CONDITIONS | MIN                     | TYP | MAX  | UNIT |  |  |  |  |

|-----------------------|---------------------------------------|-----------------|-------------------------|-----|------|------|--|--|--|--|

|                       |                                       | Standard mode   | 0                       |     | 100  |      |  |  |  |  |

| $f_{SCL}$             | SCL clock frequency                   | Fast mode       | 0                       |     | 400  | kHz  |  |  |  |  |

|                       |                                       | Fast mode plus  | 0                       |     | 1000 |      |  |  |  |  |

|                       |                                       | Standard mode   | 4.7                     |     |      |      |  |  |  |  |

| $t_{LOW}$             | LOW period of the SCL clock           | Fast mode       | 1.3                     |     | 4    | μS   |  |  |  |  |

|                       |                                       | Fast mode plus  | 0.5                     |     |      |      |  |  |  |  |

|                       |                                       | Standard mode   | 4.0                     |     |      |      |  |  |  |  |

| t <sub>HIGH</sub>     | HIGH period of the SCL clock          | Fast mode       | 0.6                     |     |      | μS   |  |  |  |  |

|                       |                                       | Fast mode plus  | 0.26                    |     |      |      |  |  |  |  |

|                       | Post front front between a GTOP and   | Standard mode   | 4.7                     |     |      |      |  |  |  |  |

| $t_{BUF}$             | Bus free time between a STOP and      | Fast mode       | 1.3                     |     |      | μS   |  |  |  |  |

|                       | a START condition                     | Fast mode plus  | 0.5                     |     |      |      |  |  |  |  |

|                       | 0.4                                   | Standard mode   | 4.0                     |     |      |      |  |  |  |  |

| $t_{\text{SU;STA}}$   | Set-up time for a repeated START      | Fast mode       | 0.6                     |     |      | μS   |  |  |  |  |

|                       | condition                             | Fast mode plus  | 0.26                    |     |      |      |  |  |  |  |

| t <sub>HD;STA</sub> I |                                       | Standard mode   | 4.0                     |     |      | μS   |  |  |  |  |

|                       | Hold time (repeated) START condition  | Fast mode       | 0.6                     |     |      |      |  |  |  |  |

|                       |                                       | Fast mode plus  | 0.26                    |     |      |      |  |  |  |  |

|                       |                                       | Standard mode   | 250                     |     |      |      |  |  |  |  |

| $t_{\text{SU;DAT}}$   | Data set-up time                      | Fast mode       | 100                     |     |      | nS   |  |  |  |  |

|                       |                                       | Fast mode plus  | 50                      |     |      |      |  |  |  |  |

|                       |                                       | Standard mode   | 0                       |     |      |      |  |  |  |  |

| $t_{\text{HD;DAT}}$   | Data hold time                        | Fast mode       | 0                       |     |      | μS   |  |  |  |  |

|                       |                                       | Fast mode plus  | 0                       |     |      |      |  |  |  |  |

|                       |                                       | Standard mode   |                         |     | 1000 |      |  |  |  |  |

| t <sub>r</sub>        | Rise time of both SDA and SCL signals | Fast mode       | 20                      |     | 300  | nS   |  |  |  |  |

|                       |                                       | Fast mode plus  |                         |     | 120  |      |  |  |  |  |

| 4                     |                                       | Standard mode   |                         |     | 300  |      |  |  |  |  |

| t <sub>f</sub>        | Fall time of both SDA and SCL signals | Fast mode       | 20×V <sub>DD</sub> /5.5 |     | 300  | nS   |  |  |  |  |

|                       |                                       | Fast mode plus  | 20×V <sub>DD</sub> /5.5 |     | 120  |      |  |  |  |  |

|                       |                                       | Standard mode   | 4.0                     |     |      |      |  |  |  |  |

| t <sub>su;sto</sub>   | Set-up time for STOP condition        | Fast mode       | 0.6                     |     |      | μS   |  |  |  |  |

|                       |                                       | Fast mode plus  | 0.26                    |     |      | 1    |  |  |  |  |

|                       |                                       | Standard mode   |                         |     | 3.45 |      |  |  |  |  |

| $t_{\text{VD;DAT}}$   | Data valid time                       | Fast mode       |                         |     | 0.9  | μS   |  |  |  |  |

| TVD,DAI               |                                       | Fast mode plus  | 1                       |     |      | 1    |  |  |  |  |

Tel: + 1 408 567 3000 Fax: + 1 408 567 3001

# **Timing Requirements (continued)**

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted)

|                      | PARAMETER                         | TEST CONDITIONS    | MIN | TYP | MAX  | UNIT |  |  |  |

|----------------------|-----------------------------------|--------------------|-----|-----|------|------|--|--|--|

|                      |                                   | Standard mode      |     |     | 3.45 |      |  |  |  |

| t <sub>VD;ACK</sub>  | Data valid acknowledge time       | Fast mode          |     |     | 0.9  | μS   |  |  |  |

|                      |                                   | Fast mode plus     |     |     | 0.45 |      |  |  |  |

|                      |                                   | Standard mode      |     |     | 400  |      |  |  |  |

| Сь                   | Capacitive load for each bus line | Fast mode          |     |     | 400  | pF   |  |  |  |

|                      |                                   | Fast mode plus     |     |     | 550  |      |  |  |  |

| t <sub>W(VSEL)</sub> | VSEL pulse duration               | VSEL = high or low |     | 5   |      | μS   |  |  |  |

# **Switching Characteristics**

$V_{IN} = 3.6 \text{ V}$ ,  $V_{OUT} = 3.3 \text{ V}$ , Typical values are at  $T_J = 25^{\circ}\text{C}$ , unless otherwise noted.

|                      | PARAMETER                                    | TEST CONDITIONS                                 | MIN | TYP  | MAX | UNIT   |

|----------------------|----------------------------------------------|-------------------------------------------------|-----|------|-----|--------|

| +                    | Delay between a rising edge on the EN        | T <sub>.1</sub> = 25°C, V <sub>.1</sub> = 3.6 V | A   | 270  | 450 | μS     |

| t <sub>d(EN)</sub>   | pin and the start of the output voltage ramp | 1j - 25 G, V <sub>I</sub> - 3.0 V               |     | 270  | 450 | μο     |

| $t_{\text{d(PG)}}$   | Power-good delay                             | V₀ falling                                      |     | 50   |     | μS     |

|                      |                                              | SLEW = 00b, forced-PWM operation                |     | ±1   |     |        |

| SR                   | Slew rate of internal ramp during dynamic    | SLEW = 01b, forced-RWM operation                |     | ±2.5 |     | V/mS   |

| SK                   | voltage scaling                              | SLEW = 10b, forced-PWM operation                |     | ±5   |     | V/IIIS |

|                      |                                              | SLEW = 11b, forced-PWM operation                |     | ±10  |     |        |

| f <sub>SW</sub>      | Inductor Switching Frequency                 | no Load, PWM operation                          |     | 2.5  |     | MHz    |

|                      | Delay between rising edge of VSEL and        |                                                 |     |      | 5   | ı,c    |

| t <sub>d(VSEL)</sub> | start of DVS ramp                            |                                                 |     |      | 5   | μS     |

Tel: + 1 408 567 3000

Fax: + 1 408 567 3001 www.ovt.com

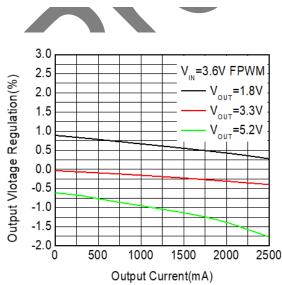

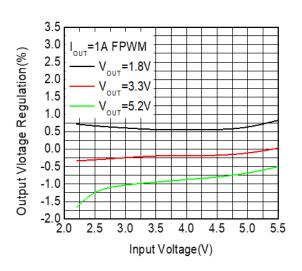

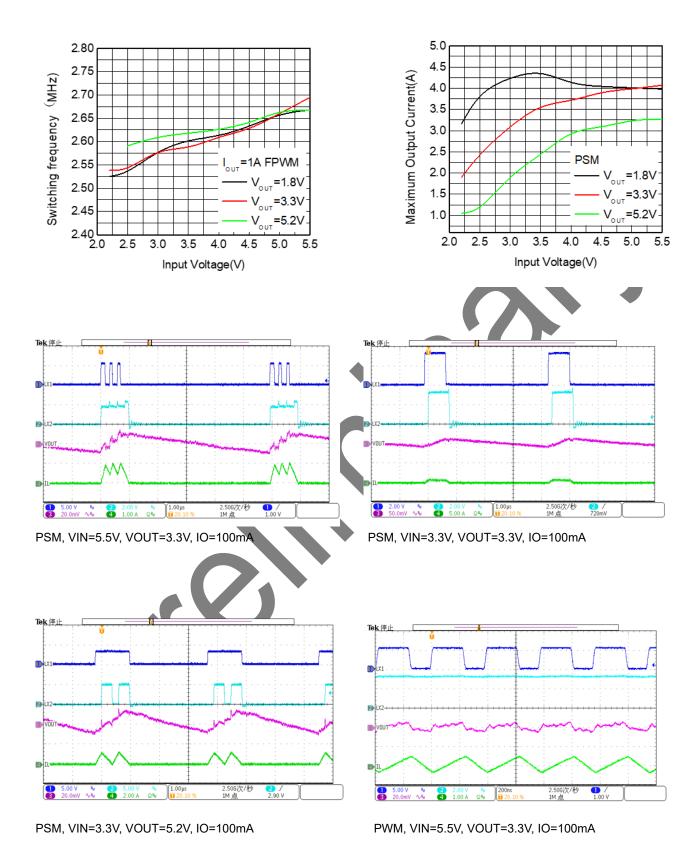

### **Typical Characteristics**

$(V_{IN} = 3.6 \text{ V}, V_{OUT} = 3.3 \text{ V}, \text{Typical values are at } T_J = 25^{\circ}\text{C}, \text{ unless otherwise noted.})$

Tel: + 1 408 567 3000 Fax: + 1 408 567 3001

www.ovt.com

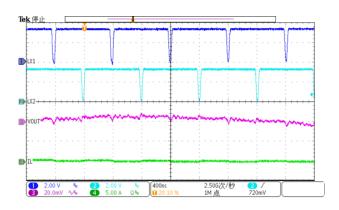

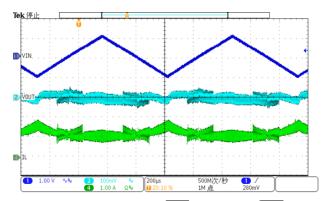

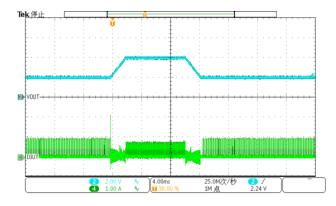

PWM, VIN=3.3V, VOUT=3.3V, IO=100mA

PWM, VIN=3.3V, VOUT=5.2V, IO=100mA

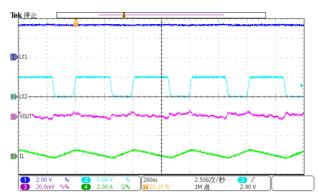

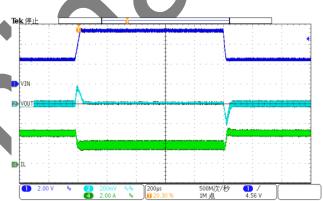

Line Transient: VIN=2.5V to 5.5V, VOUT=3.3V, IO=200mA

Line Transient: VIN=2.5V to 5.5V, VOUT=3.3V, IO=2A

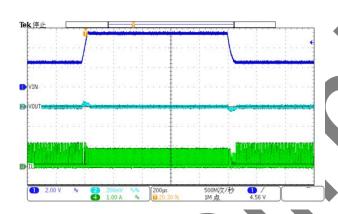

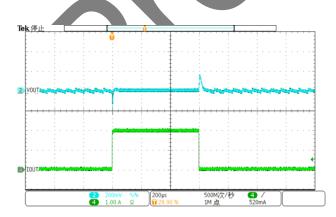

Load Transient: PSM, VIN=5.5V, VOUT=3.3V, IO=10mA to 2A

www.ovt.com

Load Transient: PSM, VIN=3.3V, VOUT=3.3V, IO=10mA to 2A

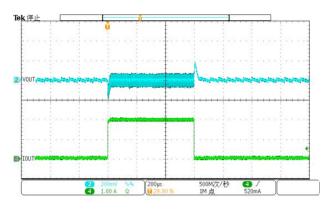

Load Transient: PSM, VIN=2.5V, VOUT=3.3V, IO=10mA to 2A

Line Sweep, FPWM, VIN= 3.3± 0.9V, VOUT=3.3V, R<sub>L</sub>=3 Ω

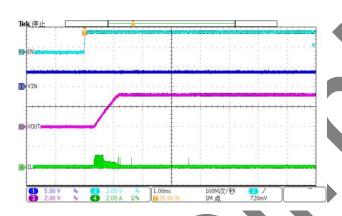

Start-up, PSM, VIN=3.6V, VQUT=3.3V, No load

Start-up, PSM, VIN=3.6V, VOUT=3.3V,  $R_L$ =3.3  $\Omega$

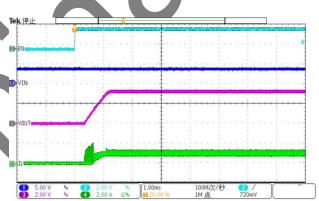

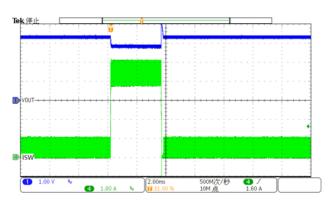

DVS, PSM, VIN=3.6V, VOUT=2V to 4V, R<sub>L</sub>=330  $\,^{\circ}$

www.ovt.com

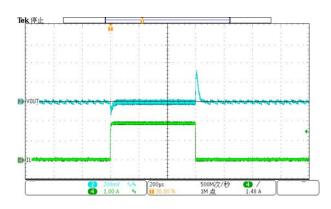

DVS, PSM, VIN=3.6V, VOUT=2V to 4V,  $R_L \! = \! 330 \, \Omega$  , RPWM

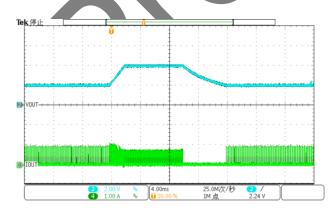

OCP, PSM, VIN=3.6V, VOUT=3.3V

OTP and Recovery, PSM, VIN=3.6V, VOUT=3.3V, RL=330  $\Omega$

# **Operation Informations**

The WD5125C is a high-efficiency buck-boost converters that integrated four switches internally to achieve high efficiency power conversion over a wide range of input voltages and output currents. It can automatically switch between buck, boost, and buck-boost operation depends on the operating conditions.

### **Feature Description**

#### **Operation Mode**

The device could automatically select the best operation mode (buck, boost or buck-boost) depends on operation conditions as showed in below figure 1.:

Figure 1. Operation Mode Selection

#### Power-Save Mode Operation (PSM)

To increase efficiency across the wide range of operating conditions, the device automatically changes from PWM at medium and high load conditions to PSM at light load condition.

To enable power-save mode, clear the FPWM bit in the Control register to 0.

PERFORMANCE PARAMETER

Low-power efficiency

Power-Save Mode (PSM)

Medium- and high-power efficiency

DC Output voltage accuracy

Transient response

Output voltage ripple

Forced-PWM

Forced-PWM

Table 1. FPWM vs. PSM Performance Comparison

#### Forced-PWM Operation (FPWM)

Tel: + 1 408 567 3000

Fax: + 1 408 567 3001

www.ovt.com

The device always operates in PWM mode if FPWM mode bit has been set in Control register. FPWM operation has lower output voltage ripple and better transient response than power-save mode operation, but lower efficiency at low output currents (see Table 1).

Note that the device inhibits forced-PWM operation during start-up (that is, until the converter output has reached power-good for the first time).

#### Enable (EN)

The EN pin enables and disables the device, high enable the device and low disable the device.

You can also use the ENABLE bit (bit 5) in the Control register to enable and disable the output of the converter (see the *Register Map*).

**Table 2. Device Enable Truth Table**

| ENABLE PIN (EN) | ENABLE BIT | DEVICE STATE                 | OUTPUT STATE            |

|-----------------|------------|------------------------------|-------------------------|

| 0               | X          | Device in Shutdown           | Output Discharge Active |

| 1               | 0          | Programming Interface Active | Output Disabled (Hi-Z)  |

| 1               | 1          | Device Active                | Output Enabled          |

#### Undervoltage Lockout (UVLO)

The device has an undervoltage lockout function that disables the device when the supply voltage is too low for correct operation.

#### **Soft Start**

To minimize inrush current and output voltage overshoot during start-up, the device has a soft-start function. At turn on, the switch current limit ramps gradually to its maximum value and the device starts up in a controlled way. The gradual increase of the current limit generates the smallest inrush current for no-load conditions. It is also possible to start into a high load as long as the load does not exceed the device current limit.

The rise time of the output voltage changes with the application circuit and the operating conditions. The output voltage rise time increases if the following occurs:

- · The output capacitance is large.

- The load current is large.

- The device operates in boost mode.

#### **Output Voltage Control**

The device supports output voltage range from 1.8 V to 5.2 V with a resolution of 25 mV. To set the needed output voltage, you must first program the RANGE bit in the Control register to select the output voltage range:

- When RANGE = 0, you can program the output voltage from 1.8 V to 4.975 V.

- When RANGE = 1, you can program the output voltage from 2.025 V to 5.2 V.

Then you can program the VOUT1 register and VOUT2 register to set the output voltage:

- When RANGE = 0, V<sub>O</sub> = (VOUT[6:0] × 0.025) + 1.8 V

- When RANGE = 1, V<sub>O</sub> = (VOUT[6:0] × 0.025) + 2.025 V

VOUT[6:0] is the 7-bit value in the VOUT1 register or VOUT2 register, whichever is active.

The VSEL pin selects which VOUT register is active:

Tel: + 1 408 567 3000

Fax: + 1 408 567 3001

www.ovt.com

- When VSEL = low, the VOUT1 register sets the output voltage.

- When VSEL = high, the VOUT2 register sets the output voltage.

To prevent output voltage transients, it is not recommended to change the output voltage range while the

converter is in operation.

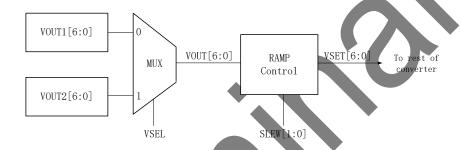

#### **Dynamic Voltage Scaling**

The device supports dynamic voltage scaling (DVS) function which lets you change the output voltage in a controlled way during operation.

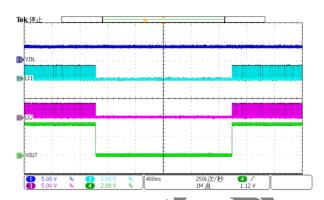

Figure 2. shows a simplified block diagram of the DVS function. The VSEL pin selects either the VOUT1 register or the VOUT2 register to control the output voltage. The ramp control block detects when the target output voltage is different from the actual output voltage and ramps the output voltage to the target voltage in 25-mV steps. 2-bit SLEW parameter in the Control register has been used to select one of four slew rates from 1 V/ms to 10 V/ms.

The device starts a DVS ramp when you change the logic level on the VSEL pin or program to a new value in the active VOUT register.

Note that if you change the contents of the active VOUT register or change the state of the VSEL pin during start-up (that is, before the end of the soft start), the converter uses the new value immediately and does not ramp gradually to the final value.

Dynamic Voltage Scaling Block Diagram Figure 2.

Note that if you change the contents of the active VOUT register or change the state of the VSEL pin during start-up (that is, before the end of the soft start), the converter uses the new value immediately and does not ramp gradually to the final value.

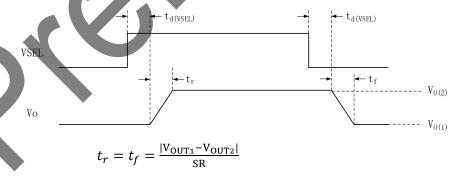

Figure 3 shows the timing diagram when you use the VSEL pin to change between the output voltage values in the VOUT1 and VOUT2 registers

#### Where:

Tel: + 1 408 567 3000

Fax: + 1 408 567 3001

www.ovt.com

- VO(1) is the output voltage set by the VOUT1 register

- VO(2) is the output voltage set by the VOUT2 register

- SR is the slew rate set by the SLEW bits in the CONTROL register

Figure 3. DVS Timing Diagram Using the VSEL Pin

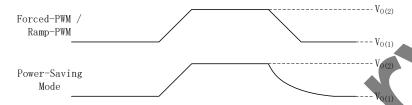

#### Ramp-PWM Operation (RPWM)

If you want the device to operate in power-save mode, but you want to make sure that dynamic voltage scaling ramps the output voltage up and down in a controlled way, Ramp-PWM operation need to be enabled. The device operates in forced-PWM when it ramps from one output voltage to another during dynamic voltage scaling. If the device operates in power-save mode and Ramp-PWM is disabled, the device cannot always control the ramp from a higher output voltage to a lower output voltage, because in power-save mode the device cannot sink current (see Figure 4).

To enable Ramp-PWM operation, set the RAMP bit (bit2) in the Control register to 1. To disable Ramp-PWM operation, clear the RAMP bit in the Control register to 0.

Ramp-PWM Operation

#### **Protection Functions**

#### Input Voltage Protection $(V_{INOV})$

Under certain operating conditions, current can flow from the output of the device to the input. For example, this can occur during dynamic voltage scaling when the output ramps down to a lower voltage and the VOUT pin sinks current from the output capacitor. Under such conditions, if the voltage source supplying the device cannot sink current, the voltage on the VIN pin can rise uncontrollably.

To make sure the input voltage stays within the permitted range, the device stops switching if the voltage on the VIN pin is greater than 5.7 V. The device automatically starts to switch again when the voltage on the VIN pin is less than 5.7 V.

# Current Limit Mode and Overcurrent Protection

Tel: + 1 408 567 3000

Fax: + 1 408 567 3001

www.ovt.com

The device has a clamp circuit which limits the peak inductor current in the event of an overload. The exact value of the output current during an overload changes with the operating conditions  $(V_l \text{ and } V_O)$  and the switching mode (buck, buck-boost, or boost).

Overloads increase the power dissipation in the device, which increases its temperature. If the device becomes too hot, the thermal shutdown function turns off the converter. When the device cools down, the thermal shutdown function automatically turns on the converter again. Thus, under a permanent overload condition, the device can periodically turn on and off, as it cools down and then heats up.

#### Thermal Shutdown

The device has a thermal shutdown function which turns off the converter if the junction temperature is greater than 155°C. The device automatically turns on the converter again when the junction temperature is less than 135°C.

When the device detects an overtemperature condition, it sets the TSD bit in the Status register to 1. The device clears the TSD bit to 0 if you read the Status register when the junction temperature of the device is less than 135°C.

#### Power Good

The device has a power-good function which indicates if the output of the DC/DC converter is in regulation or not. The device detects a power-good condition when the output voltage is greater than 95% of its nominal

value and detects a power-not-good condition when the output voltage is less than 90% of its nominal value.

When a power-not-good condition occurs, the device sets the /PG bit in the Status register to 1. The device clears the /PG bit to 0 if you read the Status register when a power-good condition exists.

#### Load Disconnect

The input is disconnected from the output when the device is shut down. This prevents any current flow from the output to the input or from the input to the output.

Tel: + 1 408 567 3000

Fax: + 1 408 567 3001

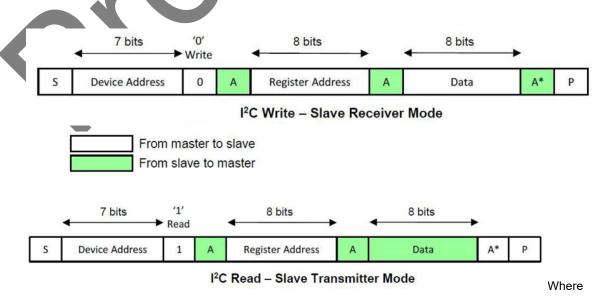

# I<sup>2</sup>C Interface

#### **Interface Overview**

The WD5125C utilizes I2C interface to write / read internal registers. It supports up to 1000Kbps fast mode plus. The 7-bit I2C address is 0x75H.

#### **Data Transactions**

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit (MSB) first. After each byte, an Acknowledge signal must follow.

Depending upon the state of the R/W bit, two types of data transfer are possible: Slave Receiver Mode (Write Mode) or Slave Transmitter Mode (Read Mode). The following figures provide more information on this process.

The 7-bit slave device address is 1110101 binary (or 75H).

Tel: + 1 408 567 3000

Fax: + 1 408 567 3001

www.ovt.com

Mar. 2021 - Rev. 0.7

18

S = START condition

P = STOP condition

Device Address = 1110101 (7 bits, MSB first)

Register Address = Reg1 – Reg5 address (8 bits)

Data = data to read or write (8 bits)

1 = Read command bit

0 = Write command bit

A = acknowledge (SDA low)

A\* = not acknowledge (SDA high)

19

# **Register Definition**

# **Register List**

| SLAVE ADDRESS | REGISTER ADDRESS | REGISTER NAME | FACTORY DEFAULT | FUNCTION  |

|---------------|------------------|---------------|-----------------|-----------|

| 0b1110101     | 0x01             | CONTROL       | 0x20            | Control   |

| 0b1110101     | 0x02             | STATUS        | 0x00            | Status    |

| 0b1110101     | 0x03             | DEVID         | 0x50            | Device ID |

| 0b1110101     | 0x04             | VOUT1         | 0x3C            | VOUT1     |

| 0b1110101     | 0x05             | VOUT2         | 0x42            | VOUT2     |

# **Register Maps**

| Address | Address Acronym |         |     |          |      | Detail   |                                               |                                     |                                            |  |  |                                  |

|---------|-----------------|---------|-----|----------|------|----------|-----------------------------------------------|-------------------------------------|--------------------------------------------|--|--|----------------------------------|

| Address | Acronym         | Name    | Bit | Field    | Туре | Reset    | Description                                   |                                     |                                            |  |  |                                  |

|         |                 |         | 7   | RESERVED | R/W  | 0        | Reserved                                      |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          |                                               |                                     | This bit selects the output voltage range. |  |  |                                  |

|         |                 |         | 6   | RANGE    | R/W  | 0        | 0: Low range (1.800 V to 4.975 V)             |                                     |                                            |  |  |                                  |

|         |                 |         |     | •        |      |          | 1 : High range (2.025 V to 5.200 V)           |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | This bit controls operation of the converter. |                                     |                                            |  |  |                                  |

|         |                 |         | 5   | ENABLE   | R/W  | 1        | 0 : Converter operation disabled              |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | 1 : Converter operation enabled               |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      | <u> </u> | This bit controls the out-of-audio function.  |                                     |                                            |  |  |                                  |

|         |                 |         |     | 4        | OOA  | R/W      | 0                                             | 0 : out-of-audio operation disabled |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | 1 : out-of-audio operation enabled            |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | This bit controls the forced-PWM function.    |                                     |                                            |  |  |                                  |

| 0x01    | CONTROL         | Control | 3   | FPWM     | R/W  | 0        | 0 : forced-PWM operation disabled             |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          |                                               |                                     |                                            |  |  | 1 : forced-PWM operation enabled |

|         |                 |         | M   |          |      |          | This bit controls the ramp-PWM function.      |                                     |                                            |  |  |                                  |

|         |                 |         | 2   | RPWM     | R/W  | 0        | 0 : ramp-PWM operation disabled               |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | 1 : ramp-PWM operation enabled                |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | These bits control the slew rate of the       |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | converter when the output                     |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | voltage setting is changed to a new value.    |                                     |                                            |  |  |                                  |

|         |                 |         | 1-0 | SLEW     | R/W  | 00       | 00b = 1.0 V/ms                                |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | 01b = 2.5 V/ms                                |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | 10b = 5 V/ms                                  |                                     |                                            |  |  |                                  |

|         |                 |         |     |          |      |          | 11b = 10 V/ms                                 |                                     |                                            |  |  |                                  |

Tel: + 1 408 567 3000 Fax: + 1 408 567 3001

# **Register Maps(continued)**

|           |         | Register              |                    |                   |      | Detail     |                                                                                                                                                                                                            |    |                                                                                                                                                                     |

|-----------|---------|-----------------------|--------------------|-------------------|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address   | Acronym | Name                  | Bit                | Field             | Туре | Reset      | Description                                                                                                                                                                                                |    |                                                                                                                                                                     |

|           |         |                       | 7-2                | RESERVED          | R    | 000000     | Reserved                                                                                                                                                                                                   |    |                                                                                                                                                                     |

| 0.00      |         |                       |                    |                   | 1    | /PG        | R                                                                                                                                                                                                          | 0  | This bit shows the status of the power-good comparator.  0: power-good  1: a power-not-good was detected                                                            |

| 0x02      | STATUS  | Status                | 0                  | TSD               | R    | 0          | This bit shows the status of the thermal shutdown function.  0: temperature good  1: an overtemperature event was detected                                                                                 |    |                                                                                                                                                                     |

|           |         |                       | 7-4                | MANUFACTURER[3:0] | R    | 0101       | These bits identify the device manufacturer.  0101 – Will Semiconductor                                                                                                                                    |    |                                                                                                                                                                     |

| 0x03      | 3 DEVID | DEVID                 | Device<br>Identity |                   | 3-2  | MAJOR[1:0] | R                                                                                                                                                                                                          | 00 | These bits identify the major silicon revision.  00: A (initial silicon)  01: B (first major revision)  10: C (second major revision)  11: D (third major revision) |

|           |         |                       | 1-0                | MINOR[1:0]        | R    | 00         | These bits identify the minor silicon revision.  00: 0 (initial silicon)  01: 1 (first minor revision)  10: 2 (second minor revision)  11: 3 (third minor revision)                                        |    |                                                                                                                                                                     |

|           |         |                       | 7                  | Reserved          | R/W  | 0          | Reserved.                                                                                                                                                                                                  |    |                                                                                                                                                                     |

| 0x04 VOUT | VOUT1   | VOUT1 Device Identity | 6-0                | VOUT1[6:0]        | R/W  | 011 1100   | These bits set the output voltage when the VSEL pin is low.  VOUT = 1.800 + (VOUT1[6:0] × 0.025) V  (low range) (default = 3.3 V)  VOUT = 2.025 + (VOUT1[6:0] × 0.025) V  (high range) (default = 3.525 V) |    |                                                                                                                                                                     |

|           |         |                       | 7                  | Reserved          | R/W  | 0          | Reserved.                                                                                                                                                                                                  |    |                                                                                                                                                                     |

| 0x05      | VOUT2   | Device<br>Identity    | 6-0                | VOUT2[6:0]        | R/W  | 100 0010   | These bits set the output voltage when the VSEL pin is high.  VOUT = 1.800 + (VOUT2[6:0] × 0.025) V (low range) (default = 3.45 V)  VOUT = 2.025 + (VOUT2[6:0] × 0.025) V (high range) (default = 3.675 V) |    |                                                                                                                                                                     |

Mar. 2021 - Rev. 0.7

21

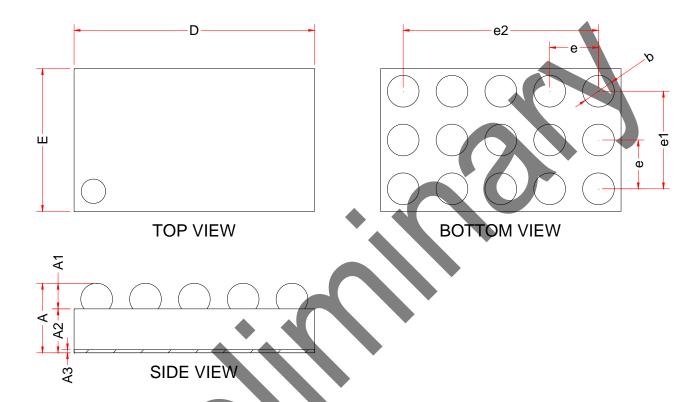

### PACKAGE OUTLINE DIMENSIONS

# CSP-15L

| Symbol | Dimensions in Millimeters |      |              |  |  |  |

|--------|---------------------------|------|--------------|--|--|--|

| Symbol | Min.                      | Тур. | Max.         |  |  |  |

| A      | 0.51                      | 0.56 | 0.61         |  |  |  |

| A1     | 0.19                      | 0.21 | 0.23<br>0.38 |  |  |  |

| A2     | 0.32                      | 0.35 |              |  |  |  |

| A3     | 0.025REF                  |      |              |  |  |  |

| b      | 0.24                      | 0.26 | 0.28         |  |  |  |

| D      | 1.94                      | 1.97 | 2.00         |  |  |  |

| Е      | 1.14                      | 1.17 | 1.20         |  |  |  |

| е      | 0.40BSC                   |      |              |  |  |  |

| e1     | 0.80BSC                   |      |              |  |  |  |

| e2     | 1.60BSC                   |      |              |  |  |  |

Tel: + 1 408 567 3000 Fax: + 1 408 567 3001

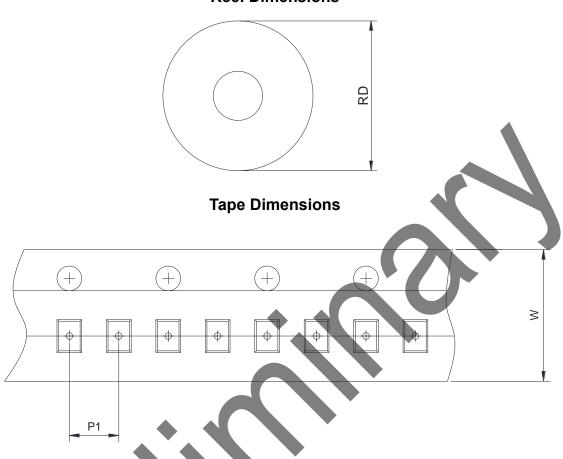

### TAPE AND REEL INFORMATION

# **Reel Dimensions**

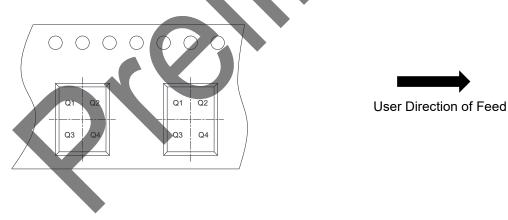

# **Quadrant Assignments For PIN1 Orientation In Tape**

| RD   | Reel Dimension                          | <b>✓</b> 7inch | 13inch |       |      |

|------|-----------------------------------------|----------------|--------|-------|------|

| W    | Overall width of the carrier tape       | <b>✓</b> 8mm   | ☐ 12mm |       |      |

| P1   | Pitch between successive cavity centers | ☐ 2mm          | ✓ 4mm  | ☐ 8mm |      |

| Pin1 | Pin1 Quadrant                           | <b>₹</b> Q1    | □ Q2   | ☐ Q3  | □ Q4 |

Mar. 2021 - Rev. 0.7

Tel: + 1 408 567 3000 Fax: + 1 408 567 3001