### **WD1072VA**

# 2A Step Down Converter with Forced PWM Feature

# **Descriptions**

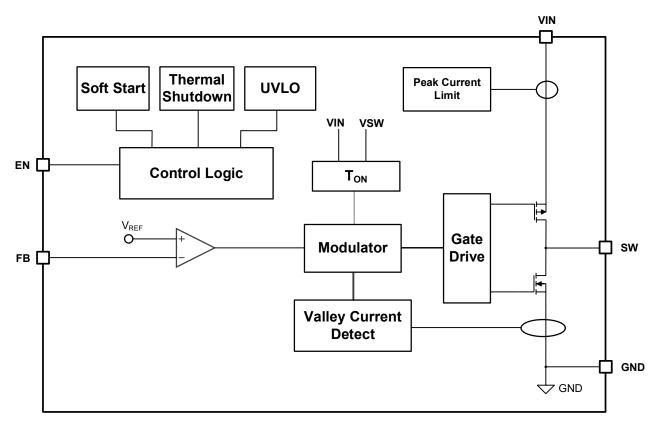

WD1072VA is a synchronous step-down DC-DC converters optimized for high efficiency and compact solution size. The device integrates switches capable of delivering an output current up to 2 A. At the whole load range, the device operates in quasi fixed frequency constant on time mode with 1.5MHz switching frequency. In shutdown, the current consumption is reduced to less than 2  $\mu$ A.

An internal soft start circuit limits the inrush current during startup. Other features like over current protection, and thermal shutdown protection are built-in.

The WD1072VA is available in SOT-563 package. Standard product is Pb-free and Halogen-free.

### **Features**

- Input voltage range of 2.5V to 5.5V

- Forced PWM to Reduce Output Voltage Ripple

- Up to 95% Efficiency

- Integrate  $125m\Omega$  (High Side) /  $65m\Omega$  (Low Side) Low R<sub>DS(ON)</sub> Power MOSFETs

- Adjustable Output Voltage from 0.6 V to VIN

- 100% Duty Cycle for Lowest Dropout

- 1.5MHz Typical Switching Frequency

- Over-current protection and Hiccup

- Thermal Shutdown Protection

# **Applications**

- General Purpose POL Supply

- Set Top Box

- Network Video Camera

- Wireless Router

- Solid State Driver / Hard Disk Driver

### Http//:www.ovt.com

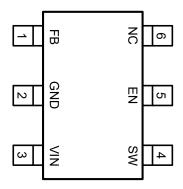

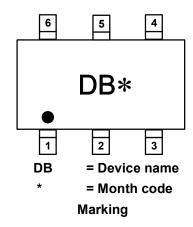

**SOT-563**

Pin configuration (Top view)

## **Order information**

| Device        | Package | Shipping       |

|---------------|---------|----------------|

| WD1072VA-6/TR | SOT-563 | 3000/Reel&Tape |

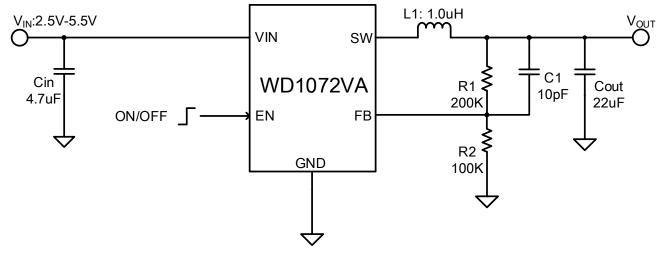

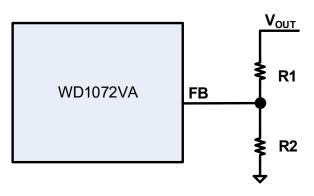

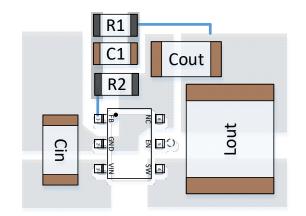

# **Typical Applications**

Fig1 Schematic Diagram

# **Pin Descriptions**

| No.                                                                                                                                                   | Symbol | Description                                                                                                                                                                                                                                  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                                                                                                                                                     | FB     | Converter feedback input. Connect to output voltage with feedback resistor divider.                                                                                                                                                          |  |

| 2 GND System Ground pin. Reference ground of the regulated output voltage: requires extra car PCB layout. Connect to GND with copper traces and vias. |        |                                                                                                                                                                                                                                              |  |

| 3                                                                                                                                                     | VIN    | Supply Voltage pin. Requires a cap to decouple the input rail. Connect using a wide PCB trace.                                                                                                                                               |  |

| 4                                                                                                                                                     | sw     | Switch pin connected to the internal FET switches and inductor terminal. Connect the inductor of the output filter using a wide PCB trace to this pin.                                                                                       |  |

| 5                                                                                                                                                     | EN     | Device enable logic input. Logic high enables the device, logic low disables the device and turns it into shutdown. Do not leave floating. To active high for automatic start-up, EN can be connected to VIN directly or through a resistor. |  |

| 6                                                                                                                                                     | NC     | No connection. Recommend to connect this pin to Ground net for better thermal performance.                                                                                                                                                   |  |

# **Block Diagram**

# Absolute Maximum Ratings(1)

| Symbol                               | Characteristics                                                                          | Rating                   | Unit |  |

|--------------------------------------|------------------------------------------------------------------------------------------|--------------------------|------|--|

| V <sub>IN</sub> ,V <sub>EN</sub>     | -                                                                                        | -0.3 ~ 6                 | V    |  |

| Vsw(DC)                              | Switch Output                                                                            | $-0.3 \sim V_{IN} + 0.3$ | V    |  |

| V <sub>SW</sub> (AC, less than 10ns) | Switch Output                                                                            | -3.0 ~ 9                 | V    |  |

| V <sub>FB</sub>                      | Output Voltage Feedback                                                                  | -0.3 ~ 3                 | V    |  |

| TJ                                   | Operation Junction Temperature                                                           | -40 ~ 150                | ℃    |  |

| $	heta_{J\!A}$                       |                                                                                          | 142                      | °C/W |  |

| Өлс                                  |                                                                                          | 51                       |      |  |

| $T_{stg}$                            | Storage Temperature                                                                      | -65 ~150                 | ℃    |  |

| НВМ                                  | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>           | ±2000                    | V    |  |

| CDM                                  | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500                     | V    |  |

Note (1): Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **Recommended Operation Conditions**

| Symbol | Characteristics          | Min      | Тур | Max | Unit |

|--------|--------------------------|----------|-----|-----|------|

| Vin    | Supply Voltage           | 2.5      |     | 5.5 | V    |

| Vouт   | Output Voltage           | $V_{FB}$ |     | Vin | V    |

| Іоит   | Output Current           | 0        |     | 2   | Α    |

| TJ     | Operating Junction Temp. | -40      | -   | 125 | °C   |

4275 Burton Drive Santa Clara, CA 95054 Tel: + 1 408 567 3000 Fax: + 1 408 567 3001 www.ovt.com

# Electronics Characteristics (Ta=25°C, V<sub>IN</sub>=5V, unless otherwise noted)<sup>(2)</sup>

| Description                                       | Symbol              | Test Condition                                   | Min | Тур   | Max  | Units |

|---------------------------------------------------|---------------------|--------------------------------------------------|-----|-------|------|-------|

| Supply Current (Shutdown)                         | I <sub>SD</sub>     | V <sub>EN</sub> = 0V                             |     | 0.01  | 2    | μA    |

| Supply Current (Quiescent)                        | IQ                  | $V_{EN} = 2V, V_{FB} = 0.5V$                     |     | 500   |      | uA    |

| HS Switch-On Resistance                           | R <sub>on_HS</sub>  | Isw=100mA , V <sub>IN</sub> =3.6V                |     | 125   |      | mΩ    |

| LS Switch-On Resistance                           | R <sub>on_LS</sub>  | I <sub>SW</sub> = -100mA , V <sub>IN</sub> =3.6V |     | 65    |      | mΩ    |

| Current Limit                                     | Ішм                 | High-side FET current limit                      | 3   |       |      | Α     |

| Switching Frequency                               | Fsw                 |                                                  |     | 1500  |      | kHz   |

| Max Duty Cycle                                    | D <sub>MAX</sub>    |                                                  | 100 |       |      | %     |

| Foodback Voltage                                  | V                   | TJ= 25°C                                         | 594 | - 600 | 606  | mV    |

| Feedback Voltage                                  | V <sub>REF</sub>    | T <sub>J</sub> = -40°C to 125°C                  | 588 | - 600 | 612  |       |

| Feedback Current                                  | I <sub>FB</sub>     | V <sub>FB</sub> =0.63V                           |     | 50    | 100  | nA    |

| EN Rising Threshold                               | VEN_RISING          |                                                  | 1.2 |       |      | V     |

| EN Falling Threshold                              | VEN_FALLING         |                                                  |     |       | 0.4  | V     |

| EN Input Current                                  | I <sub>EN</sub>     | V <sub>EN</sub> =2V                              |     | 0.4   |      |       |

| EN Input Guilent                                  | IEN                 | V <sub>EN</sub> =0V                              |     | 0     |      | - μΑ  |

| VIN Under Voltage Lockout<br>Threshold            | INUV <sub>TH</sub>  | Rising                                           |     | 2.3   | 2.45 | V     |

| VIN Under Voltage Lockout<br>Threshold Hysteresis | INUV <sub>HYS</sub> |                                                  |     | 100   |      | mV    |

| Soft-Start Period                                 | T_SS                |                                                  |     | 1.2   |      | ms    |

| Thermal Shutdown                                  | T_SD                |                                                  |     | 175   |      | °C    |

| Thermal Hysteresis                                | TSD_HYS             |                                                  |     | 30    |      | °C    |

Note (2): Guaranteed by design and engineering sample characterization.

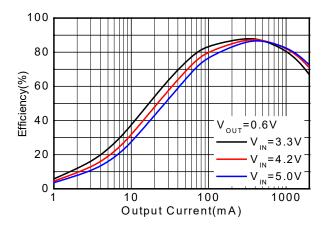

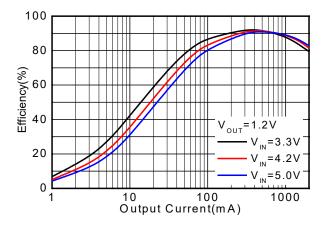

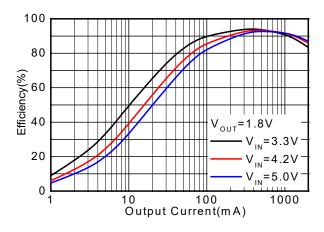

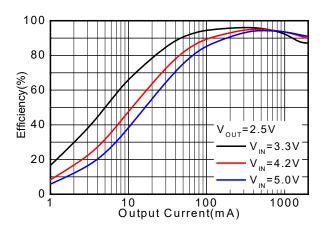

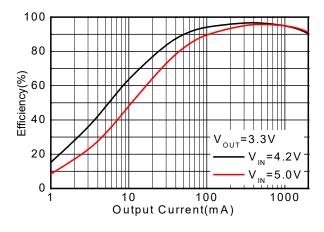

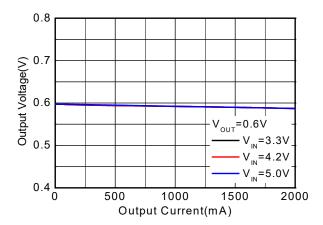

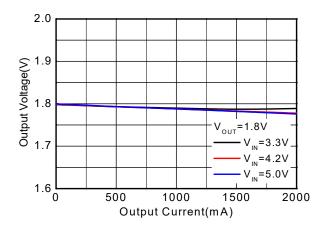

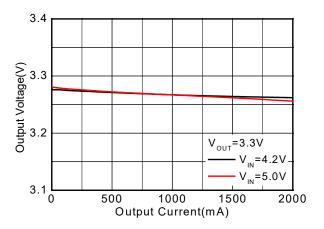

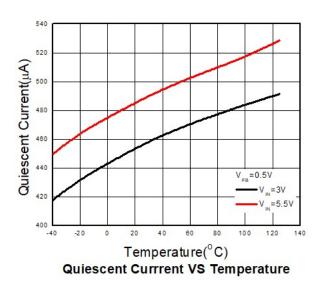

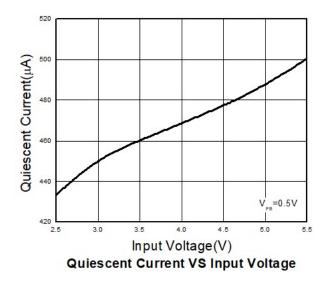

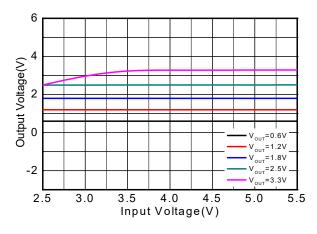

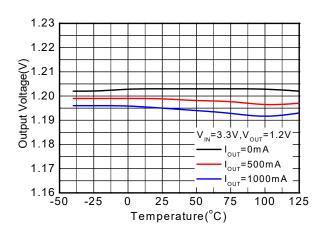

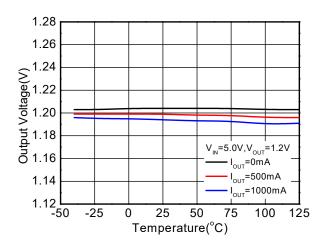

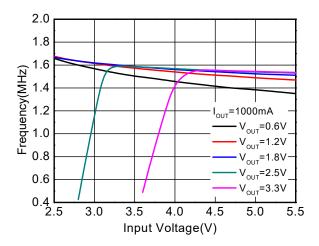

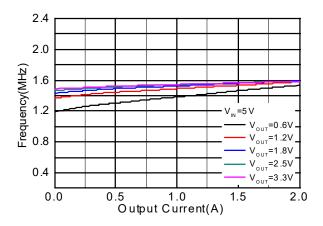

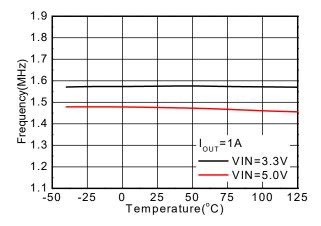

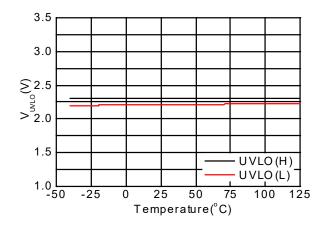

# **Typical Characteristics**

$(V_{IN}=5V, V_{OUT}=1.8V, L=1.0\mu H, C_{IN}=4.7uF, C_{OUT}=22uF, T_A=+25^{\circ}C, unless otherwise noted)$

4275 Burton Drive Santa Clara, CA 95054 Tel: + 1 408 567 3000 Fax: + 1 408 567 3001 www.ovt.com

4275 Burton Drive Santa Clara, CA 95054 Tel: + 1 408 567 3000 Fax: + 1 408 567 3001 www.ovt.com

4275 Burton Drive Santa Clara, CA 95054 Tel: + 1 408 567 3000 Fax: + 1 408 567 3001 www.ovt.com

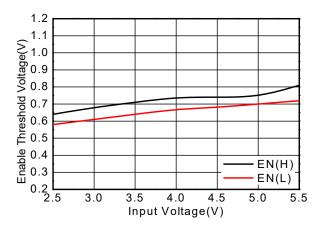

Switching waveform, V<sub>IN</sub>= 3.3V,V<sub>OUT</sub>=1.2V,I<sub>OUT</sub>=2A

Switching waveform, VIN= 5.0V, VOUT=1.2V, IOUT=2A

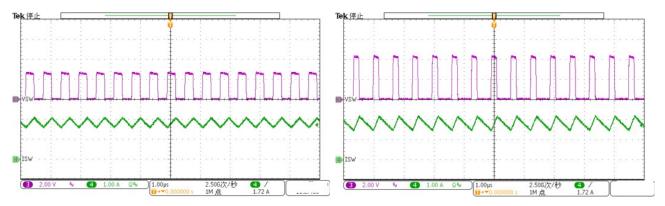

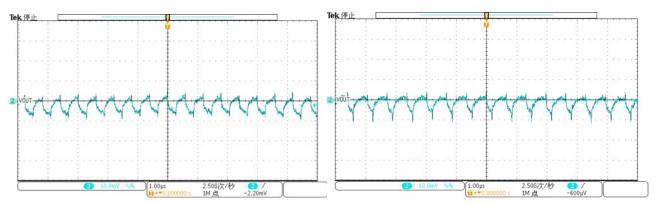

Ripple,  $V_{IN}$ = 3.3V, $V_{OUT}$ =1.2V, $I_{OUT}$ =2A

Ripple,  $V_{IN}$ = 5.0V, $V_{OUT}$ =1.2V, $I_{OUT}$ =2A

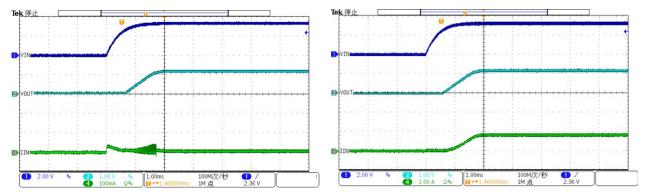

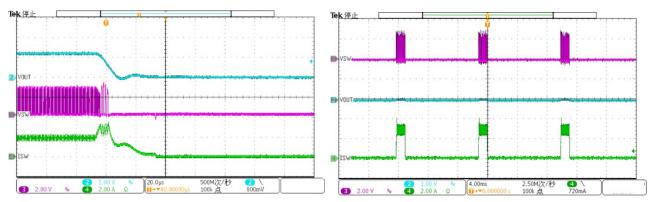

Start up from  $V_{IN}$ ,  $V_{IN}$ = 3.3V, $V_{OUT}$ =1.2V, $I_{OUT}$ =0A

Start up from  $V_{IN}$ ,  $V_{IN}$ = 3.3V, $V_{OUT}$ =1.2V, $I_{OUT}$ =2A

4275 Burton Drive Santa Clara, CA 95054 USA

Tel: + 1 408 567 3000 Fax: + 1 408 567 3001 www.ovt.com

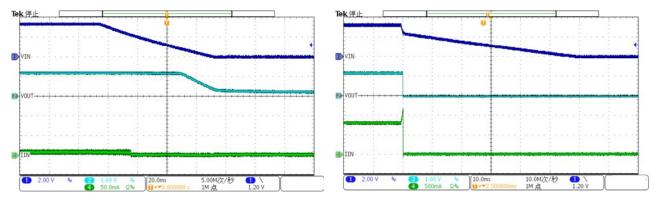

Shut down from  $V_{IN}$ ,  $V_{IN}$ = 3.3V, $V_{OUT}$ =1.2V, $I_{OUT}$ =0A

Shut down from  $V_{IN}$ ,  $V_{IN}$ = 3.3V, $V_{OUT}$ =1.2V, $I_{OUT}$ =2A

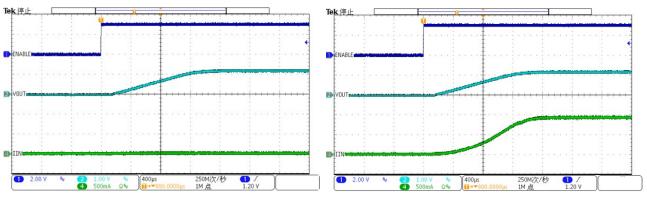

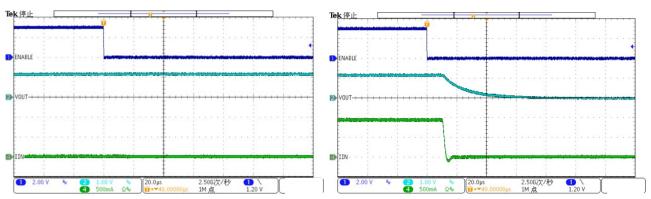

Start up from EN,  $V_{IN}$ = 3.3V, $V_{OUT}$ =1.2V, $I_{OUT}$ =0A

Start up from EN,  $V_{IN}$ = 3.3V, $V_{OUT}$ =1.2V, $I_{OUT}$ =2A

Shut down from EN,  $V_{IN}$ = 3.3V, $V_{OUT}$ =1.2V, $I_{OUT}$ =0A

Shut down from EN,  $V_{IN}$ = 3.3V, $V_{OUT}$ =1.2V, $I_{OUT}$ =2A

4275 Burton Drive Santa Clara, CA 95054 Tel: + 1 408 567 3000 Fax: + 1 408 567 3001 www.ovt.com

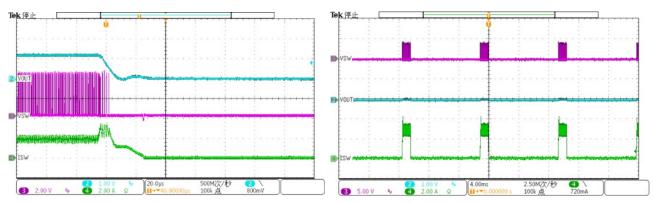

V<sub>IN</sub>= 3.3V, V<sub>OUT</sub>=1.2V, I<sub>OUT</sub>=2A~Short to GND

$V_{IN}$ = 5.0V,  $V_{OUT}$ =1.2V,  $I_{OUT}$ =2A~Short to GND

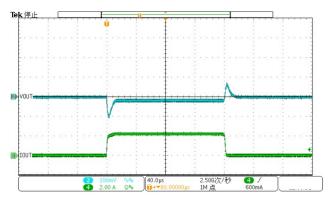

Load Transient, V<sub>IN</sub>=3.3V, V<sub>OUT</sub>=1.5V, I<sub>OUT</sub> 1mA to 2000mA

## **Operation Informations**

The WD1072VA is a high-efficiency FPWM synchronous step-down converter. The device operates with an adaptive on time with valley current control scheme. The device operates at typically 1.5MHz frequency Constant On time mode. Basing on the  $V_{\text{IN}}/V_{\text{OUT}}$  ratio, internal circuit sets required on time for high side MOSFET. It makes the switching frequency relatively constant regardless of the variation of input voltage, output voltage, and load current.

### **Enabling/Disabling the Device**

The WD1072VA is enabled by setting the EN input to a logic High. Accordingly, a logic Low disables the device. If the device is enabled, the internal power stage starts switching and regulates the output voltage to the set point voltage. The EN input must be terminated and should not be left floating.

## 100% Duty Cycle Low Dropout Operation

The WD1072VA offers 100% duty cycle operation mode. In this mode, the high-side MOSFET switch is constantly turned on and the low-side MOSFET is switched off. The minimum input voltage to maintain output regulation, depending on the load current and output voltage, is calculated as:

$V_{IN(MIN)} = V_{OUT} + I_{OUT} x (R_{DS(ON)} + R_L)$

where

- RDS(ON) = High side FET on-resistance

- RL = Inductor ohmic resistance (DCR)

### **Soft Startup**

After enabling the WD1072VA, internal soft startup circuitry ramps up the output voltage which reaches nominal output voltage in 1.2mS typically. This avoids excessive inrush current and creates a smooth output voltage rise slope. It also prevents excessive voltage drops of primary cells and rechargeable batteries with high internal impedance. The device is able to start into a pre-biased output capacitor. The converter starts with the applied bias voltage and ramps the output voltage to its nominal value.

#### **Switch Current Limit**

The switch current limit prevents the WD1072VA from high inductor current and drawing excessive current from a battery or input voltage rail. Excessive current might occur with a heavy load or shorted output circuit condition. The device adopts the peak current limit control by sensing the current of the high-side switch. Once the high-side switch current limit is reached, the high-side switch is turned off and low-side switch is turned on to ramp down the inductor current with an adaptive off-time.

#### **Under Voltage Lockout (UVLO)**

To avoid mis-operation of the WD1072VA at low input voltages, under voltage lockout is implemented that shuts down the device at voltages lower than VUVLO with VHYS\_UVLO hysteresis.

#### **Thermal Shutdown**

The WD1072VA enters thermal shutdown once the junction temperature exceeds the thermal shutdown rising threshold, T<sub>JSD</sub>. Once the junction temperature falls below the falling threshold, the device returns to normal operation automatically.

4275 Burton Drive Santa Clara, CA 95054 Tel: + 1 408 567 3000 Fax: + 1 408 567 3001 www.ovt.com

# **Application Informations**

### **Setting the Output Voltage**

The output voltage is set with a resistor divider from the output node to the FB pin. It is recommended to use 1% tolerance or better divider resistors. Start by using Equation (1) to calculate Vout. To improve efficiency at light loads consider using larger value resistors, too high of resistance will be more susceptible to noise and voltage errors from the FB input current will be more noticeable.

$$V_{\text{OUT}} = V_{\text{FB}} \times \left(1 + \frac{R1}{R2}\right) \tag{1}$$

The feedback circuit is shown in below:

## **Setting the Inductor**

An inductor is necessary to supply a constant current to the output load while being driven by the switched input voltage. A larger inductor results in less ripple current and a lower output ripple voltage, but also has a larger physical footprint, higher series resistance, and lower saturation current. A good rule for determining the inductance value is to design the peak-to-peak ripple current in the inductor to be between 30% and 40% of the maximum output current, and ensure that the peak inductor current is below the maximum switch current limit. The inductance value can be calculated with Equation (2):

$$L = \frac{V_{OUT}}{F_{SW} \times \Delta I_{L}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(2)

Where  $\Delta I_{L}$  is the peak-to-peak inductor ripple current. The inductor should not saturate under the

maximum inductor peak current. The peak inductor current can be calculated with equation (3):

$$I_{LP} = I_{OUT} + \frac{V_{OUT}}{2 \times F_{SW} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(3)

#### **Selecting the Input Capacitor**

The device requires an input decoupling capacitor and a bulk capacitor is needed depending on the application. The input current to the step-down converter is discontinuous and therefore requires a capacitor to supply AC current to the step-down converter while maintaining the DC input voltage. For the best performance, use ceramic capacitors placed as close to VIN as possible. Capacitors with X5R and X7R ceramic dielectrics are recommended because they are fairly stable with temperature fluctuations.

The capacitors must also have a ripple current rating greater than the maximum input ripple current of the converter. The input ripple current can be estimated with Equation (4):

$$I_{CIN} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

(4)

The worst-case condition occurs at  $V_{IN} = 2V_{OUT}$ , shown in Equation (5):

$$I_{CIN} = \frac{1}{2} \times I_{OUT}$$

(5)

For simplification, choose an input capacitor with an RMS current rating greater than half of the maximum load current.

The input capacitance value determines the input voltage ripple of the converter. If there is an input voltage ripple requirement in the system, choose the input capacitor that meets the specification.

The input voltage ripple can be estimated with Equation (6):

$$\Delta V_{IN} = \frac{I_{OUT}}{F_{SW} \times C_{IN}} \times \left(\frac{V_{OUT}}{V_{IN}}\right) \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(6)

The worst-case condition occurs at  $V_{IN} = 2V_{OUT}$ , shown in Equation (7):

4275 Burton Drive Santa Clara, CA 95054 Tel: + 1 408 567 3000 Fax: + 1 408 567 3001

$$\Delta V_{\rm IN} = \frac{1}{4} \times \frac{I_{\rm OUT}}{F_{\rm SW} \times C_{\rm IN}} \tag{7}$$

A ceramic capacitor over 10  $\mu F$  is recommended for the decoupling capacitor. An additional 0.1  $\mu F$  capacitor from VIN pin to ground is optional to provide additional high frequency filtering.

### **Selecting the Output Capacitor**

An output capacitor is required to maintain the DC output voltage. Ceramic or POSCAP capacitors are recommended. The output voltage ripple can be estimated with Equation (8):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{F_{\text{SW}} \times L} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times \left(R_{\text{ESR}} + \frac{1}{8 \times F_{\text{SW}} \times C_{\text{OUT}}}\right)$$

(8)

In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly caused by the capacitance. For simplification, the output voltage ripple can be estimated with Equation (9):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{8 \times F_{\text{SW}}^2 \times L \times C_{\text{OUT}}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \quad (9)$$

In the case of POSCAP capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated with Equation (10):

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{F_{\text{SW}} \times L} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times R_{\text{ESR}}$$

(10)

#### **PC Board Layout Considerations**

A good circuit board layout aids in extracting the most performance from the WD1072VA. Poor circuit layout degrades the output ripple and EMI or EMC performance.

The evaluation board layout is optimized for the WD1072VA. Use this layout for best performance. If this layout needs changing, use the following guidelines:

Use wide and short traces for power paths (such as VIN, SW and GND) to improve efficiency and reduce parasitic inductance.

- The input low-ESR ceramic capacitor should be connected to the VIN and GND pin as close as possible to the IC.

- Arrange a "quiet" path for output voltage sense and feedback network, and make it surrounded by a ground plane once possible. Place feedback network close to IC.

- GND trace that connect Cin, GND pin, NC pin and Cout should be as short and wide as possible to minimize the trace impedance, big GND plane or layer is strongly recommended to improve thermal and noise performance.

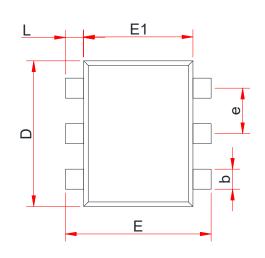

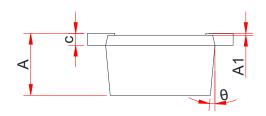

# PACKAGE OUTLINE DIMENSIONS

# **SOT-563**

**TOP VIEW**

**BOTTOM VIEW**

SIDE VIEW

| Occurred to all | Dimensions in Millimeters |             |      |  |  |  |

|-----------------|---------------------------|-------------|------|--|--|--|

| Symbol          | Min.                      | Тур.        | Max. |  |  |  |

| A               | 0.45                      | 0.52        | 0.60 |  |  |  |

| A1              | 0.00                      | _           | 0.05 |  |  |  |

| е               |                           | 0.50BSC     |      |  |  |  |

| С               | 0.09                      | _           | 0.18 |  |  |  |

| D               | 1.50                      | 1.60        | 1.70 |  |  |  |

| Е               | 1.50                      | 1.60        | 1.70 |  |  |  |

| E1              | 1.10                      | 1.10 —      |      |  |  |  |

| b               | 0.17                      | 0.17 0.22 0 |      |  |  |  |

| L               | 0.15Ref                   |             |      |  |  |  |

| L1              | 0.25Ref                   |             |      |  |  |  |

| θ               | 7° Ref                    |             |      |  |  |  |

4275 Burton Drive Santa Clara, CA 95054 USA Tel: + 1 408 567 3000 Fax: + 1 408 567 3001 www.ovt.com

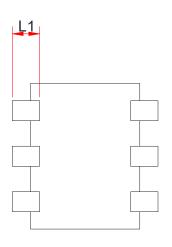

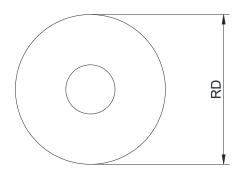

# TAPE AND REEL INFORMATION

# **Reel Dimensions**

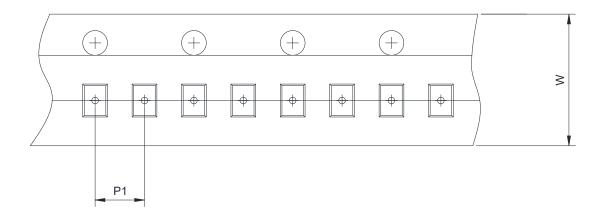

**Tape Dimensions**

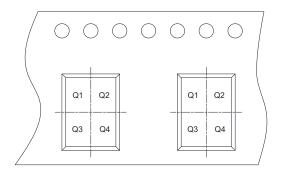

# **Quadrant Assignments For PIN1 Orientation In Tape**

| RD   | Reel Dimension                          | <b>✓</b> 7inch | 13inch |             |      |

|------|-----------------------------------------|----------------|--------|-------------|------|

| W    | Overall width of the carrier tape       | ₹ 8mm          | 12mm   | ☐ 16mm      |      |

| P1   | Pitch between successive cavity centers | 2mm            | ✓ 4mm  | 8mm         |      |

| Pin1 | Pin1 Quadrant                           | □ Q1           | □ Q2   | <b>✓</b> Q3 | □ Q4 |

4275 Burton Drive Santa Clara, CA 95054 USA Tel: + 1 408 567 3000 Fax: + 1 408 567 3001 www.ovt.com